白皮书《利用优化的硅和SOI衬底实现下一代功率和射频氮化镓器件》

凭借其优异的性能,氮化镓(GaN)成为功率和射频器件的优异材料。然而,在硅上生长高质量的氮化镓层面临着机械和热方面的挑战。本白皮书探讨了优化的硅和键合SOI衬底如何通过控制应力、减少缺陷和提高晶圆稳定性来支持可靠的氮化镓外延。此外,白皮书还重点介绍了SOI上氮化镓技术在实现集成紧凑型器件设计方面的优势。

针对氮化镓生长进行整体优化的硅衬底:旨在克服生长挑战,挑战氮化镓薄膜质量,并提升功率和射频器件性能

用于先进器件的SOI上氮化镓:将氮化镓的性能和键合SOI的隔离特性相结合,实现高效、紧凑的功率和射频解决方案的单片集成

规模化验证:迄今为止已交付近50万片晶圆产品,用于高良率氮化镓生长

引言

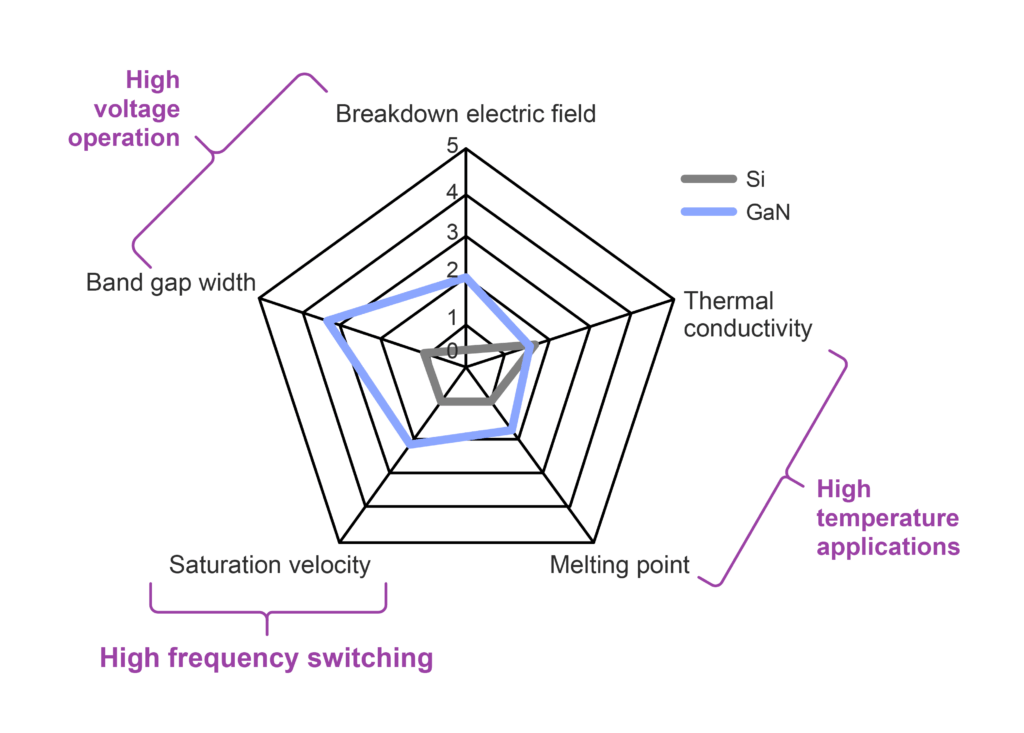

凭借其卓越的材料特性,氮化镓(GaN)在半导体行业中迅速崛起,在高功率电子器件、射频(RF)应用、LED和光电子器件中表现出色。与传统的硅基技术相比,氮化镓的宽带隙、高击穿电压和高电子迁移率使其能够在更高的电压、温度和频率下有效工作(图1)。这些特性使氮化镓成为效率、可靠性和性能至关重要的的功率和射频应用的理想选择。

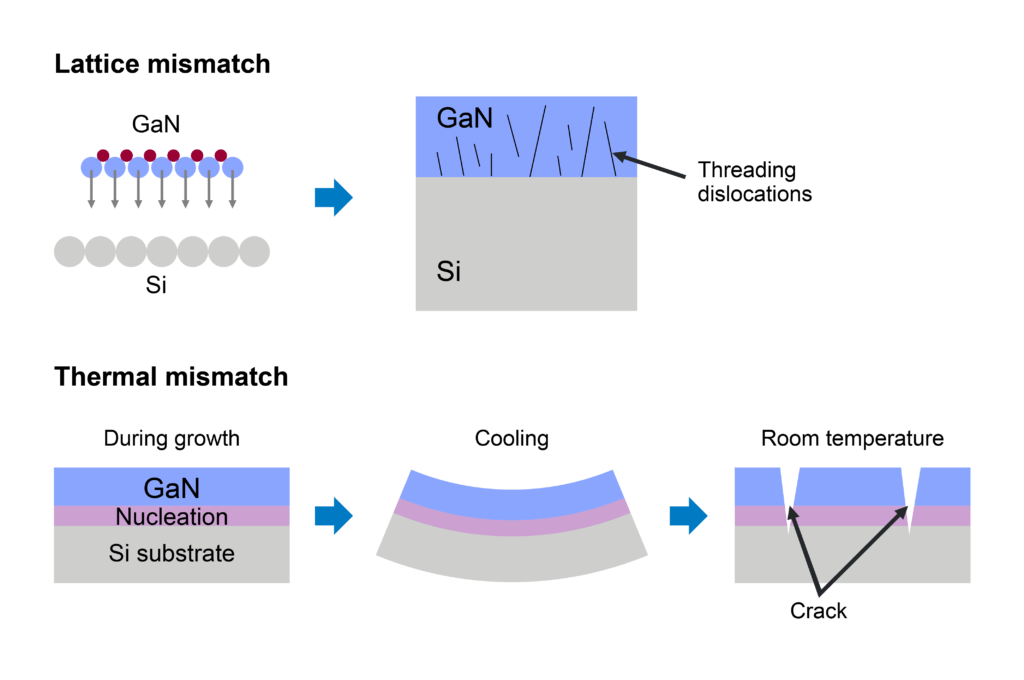

然而,在硅衬底上生长高质量的氮化镓层面临着诸多挑战。氮化镓与硅之间存在显著的晶格失配和热膨胀系数差异,这可能导致高温外延过程中位错密度高、晶圆弯曲,甚至出现裂纹。必须谨慎控制这些机械应力和热应力,以确保器件的可靠性和制造良率。

虽然硅基氮化镓和SOI上氮化镓具有成本和可扩展性上的优势,但解决晶格和热失配的固有挑战需要结合先进的缓冲层工程和优化的衬底设计。

本白皮书探讨了优化硅晶圆和键合绝缘体上硅(SOI)衬底在支持氮化镓生长方面的作用,重点介绍了它们在功率和射频器件方面的优势。虽然硅基氮化镓和SOI上氮化镓具有成本和可扩展性上的优势,但要解决晶格和热失配的固有挑战需要结合先进的缓冲层工程和优化的衬底设计。通过调整硅和SOI衬底的关键参数,譬如晶圆厚度、间隙氧浓度、边缘轮廓和电阻率,可以减轻应力、抑制缺陷形成并提高氮化镓外延过程中的机械稳定性。除了这些优势之外,SOI上氮化镓还具有单片集成的优势,能够在单个芯片上构建多种功能,并进一步简化整体期间架构。这些优势的结合使得硅和键合SOI衬底非常适合功率转换、LED器件、5G和其他高频系统中的氮化镓应用。

图1:氮化镓和硅的比较

氮化镓生长和衬底选择

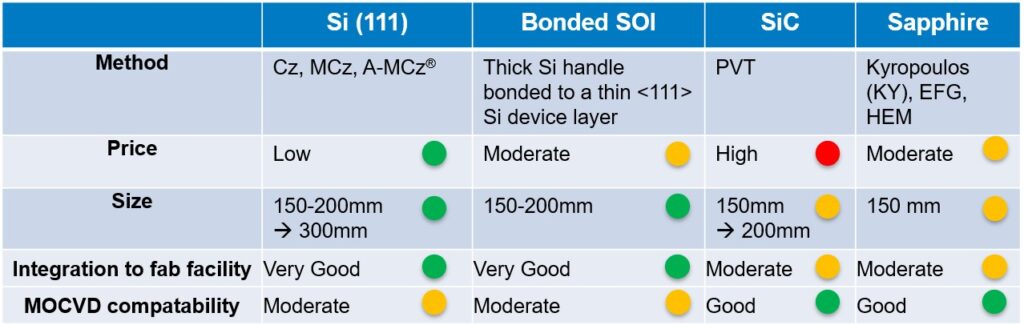

氮化镓生长对于高性能功率和射频应用日益重要。外延方法譬如金属有机化学气相沉积(MOCVD),通常用于在各种衬底上生长氮化镓,包括硅(Si)、键合绝缘体上硅(SOI)、碳化硅(SiC)和蓝宝石。如图2所示,每种衬底在氮化镓生长方面都具有独特的优势和挑战,会影响成本、热管理和晶格匹配等因素。

虽然碳化硅和蓝宝石在热失配和晶格失配方面更适合氮化镓生长,但它们价格昂贵、晶圆尺寸受限,并且难以集成到标准的硅基工艺中。

图2:用于氮化镓外延生长的不同衬底

硅是经济高效且可扩展的材料选择

与碳化硅晶圆相比,硅晶圆的价格更实惠且应用广泛,使其成为制造商的经济之选。除了材料成本更低之外,硅片还支持大规模生产,这得益于其与CMOS的兼容性以及更大的尺寸(最大可达300mm),从而增加了每片晶圆的芯片数量。成熟的硅供应链和现有的制造基础设施无需专用设备,进一步降低了成本,使硅成为硅基氮化镓技术(GaN-on-Si)的理想平台。此外,与碳化硅基氮化镓(GaN-on-SiC)[Vanhouche] 相比,硅基氮化镓制造通常更加环保,因为碳化硅生产需要更高的能耗,并且涉及更多资源密集型工艺。

除了材料成本较低之外,由于硅晶圆与CMOS兼容且尺寸更大(最大300mm),因此支持大规模生产,从而增加了每个晶圆的芯片数量。

在硅基方案中,键合绝缘体上硅(SOI)衬底已成为氮化镓生长的一种有前景的替代方案,由于外延过程中应力管理的改进,其晶体质量更高、裂纹更少 [Lemettinen]。SOI的优势包括其在单片集成功率和射频组件方面的潜力,使其成为下一代氮化镓器件平台极具吸引力的途径。

衬底优化如何协助克服硅上氮化镓的挑战

氮化镓和硅之间的热膨胀和晶格失配会在氮化镓生长和冷却过程中产生巨大的机械应力(图3)。这些应力可能导致晶圆弯曲、翘曲、开裂和位错密度升高,从而对器件性能和良率产生负面影响。解决这些机械挑战对于在硅衬底上实现高质量的氮化镓外延至关重要。

虽然外延工程(特别是缓冲层设计)对于控制应力和减少位错至关重要,但成功实现硅上氮化镓生长的一个重要因素使使用高质量、优化的硅衬底。

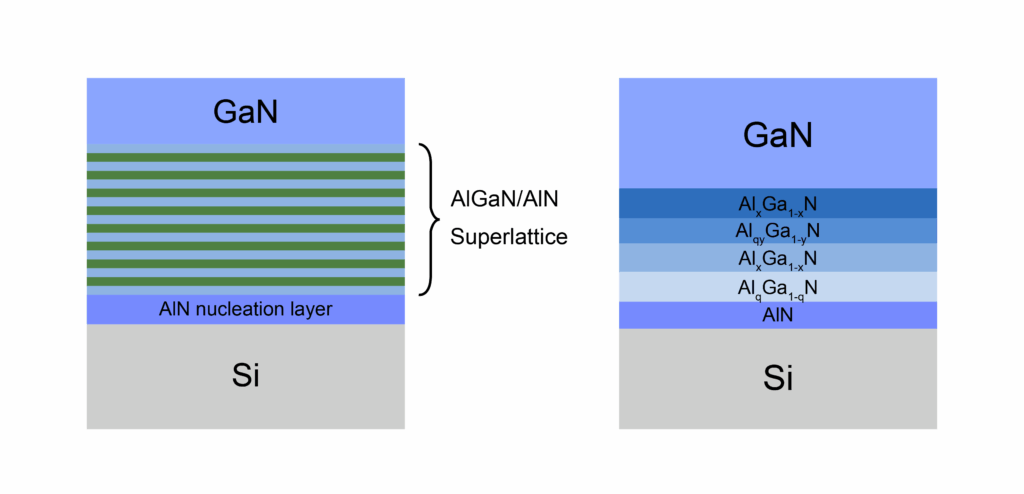

虽然外延工程,尤其是采用氮化铝(AlN)或氮化铝镓(AlGaN)等材料的缓冲层设计,对于控制应力和减少位错很关键(图4),但成功实现硅基氮化镓(GaN-on-Si)生长的一个重要因素在于使用高质量、优化的硅衬底。优化的硅衬底能够提供所需的机械稳定性和表面质量,以支持先进的外延结构并提升氮化镓薄膜的整体性能。

图3:硅基氮化镓(GaN-on-Si)的晶格和热失配。上图:氮化镓的晶格常数与硅不同(较大),这在成核过程中会引入应变。当系统试图释放应力时,这会导致诸如穿透位错之类的缺陷。下图:在高温冷却的过程中,硅的收缩程度比氮化镓更大,如果硅衬底未针对氮化镓生长进行优化,则会导致氮化镓薄膜弯曲/翘曲并形成裂纹。

图4:两种常用缓冲层设计的示意图。超晶格缓冲层(左)和阶梯渐变缓冲层(右),用于在优化的硅衬底上进行氮化镓生长。除缓冲层工程外,硅衬底的质量和优化在应力和缺陷管理方面也起着重要作用,为氮化镓外延的成功生长提供了所需的机械稳定性。超晶格缓冲层由重复的AlGaN/AlN层组成,以逐步解决晶格和热失配问题;而阶梯渐变缓冲层则通过逐层改变铝含量来缓解应变并减少晶圆弯曲。

针对高质量氮化镓外延的优化硅衬底

完整的衬底工程方法使成功实现硅基氮化镓(GaN-on-Si)生长的关键。可以微调多个衬底参数,以实现高质量的外延并减少应力相关缺陷:

- <111>晶向具有严格的表面晶向公差,有助于控制应变、减少晶格失配效应并提高良率

- 更厚的晶圆可最大限度地减少原位曲率,确保外延的均匀性

- 控制杂质(譬如Oi)可防止滑移,从而提高机械强度

- 精心设计的晶圆边缘可优化气流和热分布,从而实现工艺的一致性

- 优化的电阻率满足射频和功率器件的需求

晶向和厚度

硅通常被选作氮化镓生长的基底,尤其是<111>晶向且表面晶向紧密的硅材料。因为它有更好的晶格兼容性,有助于降低应变并提高外延过程中的晶体质量。

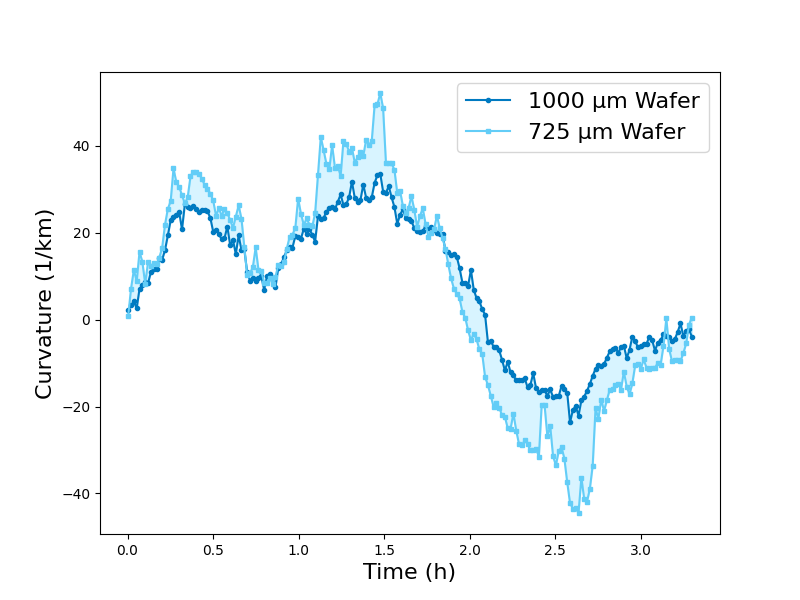

然而,由于硅和氮化镓之间晶格常数和热膨胀系数的不匹配问题比较突出,通常需要更厚的硅晶圆来控制高温加工过程中产生的机械应力和热应力。原位晶圆曲率测量可用于监测晶圆翘曲度的实时变化,从而深入了解生长过程中的应力演变和机械稳定性。

如图5所示,与厚度较薄的725 µm硅片相比,厚度较厚的1000 µm硅片的曲率演变更稳定、更平滑,而厚度较薄的725 µm硅片的曲率波动更大,曲率变化也更大。这表明增加硅片厚度可以增强氮化镓外延过程中的机械稳定性并降低曲率敏感性。更稳定的晶圆弯曲或翘曲有助于改善层的均匀度,并有助于缓解潜在的产量问题,譬如错位、局部应力或缺陷的形成。

图5:外延过程中硅片的原位曲率随时间的变化。较厚的1000 µm硅片表现出更稳定、更平滑的曲率变化,而较薄的725 µm硅片则表现出更大的波动和曲率变化。更稳定的晶圆弯曲或翘曲有助于提高层的均匀度,并有助于缓解潜在的良率问题,譬如位错、局部应力或缺陷的形成。

控制氧含量

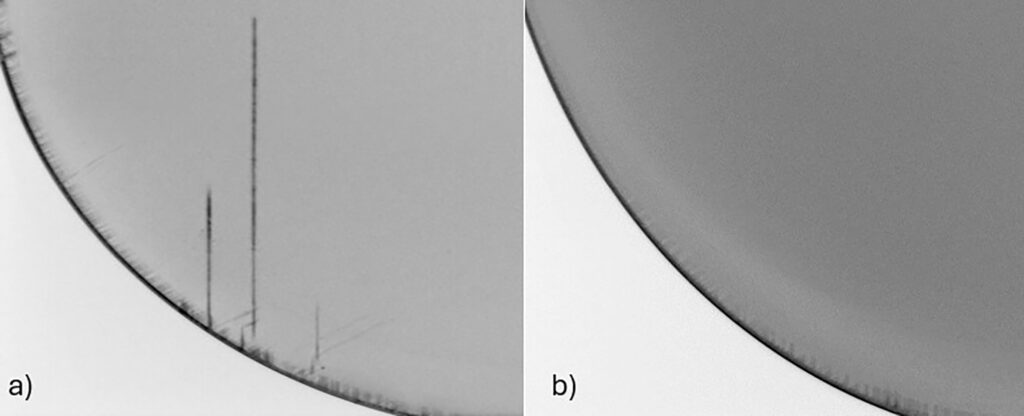

此外,精确控制硅衬底中的间隙氧(Oi)浓度对于增强机械强度和晶圆的稳定性至关重要。控制良好的Oi浓度可以增强硅片的抗滑移能力,有助于最大限度地减少翘曲,并确保在氮化镓外延的高温条件下具有更高的耐用性。滑移线是由于热应力作用下的塑性变形而形成的位错网络,滑移线的存在可能表明硅片内部存在机械损伤。

管理良好的Oi浓度可提高晶圆对滑移形成的抵抗力,有助于最大限度地减少翘曲并确保在氮化镓外延的高温条件下具有更高的耐用性。

氧沉淀物,即在热处理过程中形成的小氧原子簇,可以发挥有益作用。当它们足够小时,可以钉住位错 [Zeng, Sueoka] 并增强材料强度,使其更耐变形。这些沉淀物通常在高温处理过程中形成,此时硅晶格中过量的氧原子会迁移并聚集在一起。虽然较高的间隙氧含量往往会促进更多沉淀物的形成并改善机械性能,但必须仔细控制它们的生长,以避免引入不必要的缺陷。

如图6所示,X射线衍射成像(XRDI)分析显示优化氧指数(Oi)水平的晶圆(图6b)的滑移线明显少于未优化的晶圆(图6a),这凸显了氧指数控制对于保持晶圆完整性的重要性。更少的滑移线可增强器件性能和机械稳定性,从而确保氮化镓基应用的更高的可靠性。

图6:XRDi显示Oi优化的晶圆(b)的滑移线比(a)未优化晶圆的滑移线更少。氮化镓生长过程中滑移线减少表明应力更低,材料的质量更高。

边缘工程

晶圆的边缘工程设计在优化氮化镓外延工艺中发挥着至关重要的作用,因为它能够促进晶圆表面气流和热分布的均匀性。合理的边缘整形可以降低局部温度的梯度,并抑制可能导致膜厚不均匀或缺陷的边界相关异常。这增强了生长工艺的整体一致性,改善了外延层的均匀性、表面形貌,并最终提高了器件的良率。边缘工程设计对于大直径硅片尤为重要,因为大直径硅片的边缘效应更为明显,会影响工艺的稳定性和材料质量。

边缘工程增强了生长过程的整体一致性,改善了外延层的均匀性、表面形貌,并最终提高了器件的产量。

电阻率

硅片的电阻率在硅基氮化镓外延中起着非常重要的作用,它不仅影响生长过程,还会影响最终器件的性能。Okmetic的先进磁拉法(A-MCz®)长晶工艺可提供高质量的硅衬底,其电阻率水平经过精心调整,可满足射频和功率应用的特定要求。

Okmetic的先进磁拉法(A-MCz®)长晶工艺提供高质量的硅基材料,其电阻率水平经过精心调整,可满足射频和功率应用的特定要求。

对于功率电子应用,通常使用低电阻率硅片(通常小于0.02欧姆-厘米)。在功率器件中,外延叠层通常更厚,在加工和运行过程中需要更坚固的衬底以保持其结构的完整性。

相比之下,射频应用首选高电阻率硅片(通常大于1000欧姆-厘米),以最大限度地减少射频信号与硅衬底之间不必要的相互作用。这可以减少射频信号损耗,并增强线性度和信号完整性,这对于射频开关和功率放大器等高频、高线性度器件至关重要。

因此,选择适合的晶圆电阻率是优化硅基氮化镓器件机械和电气性能的关键,以满足在不同的目标市场需求。

SOI上氮化镓是一项新兴技术

GaN-on-SOI(绝缘体上硅基氮化镓)是一项新兴技术,在半导体应用领域正获得长足的发展,尤其在功率电子和射频器件领域。它结合了氮化镓的高性能特性以及SOI的电气隔离和机械优势,显著提升了器件效率和整体性能。GaN-on-SOI技术解决了电气隔离和降低寄生效应等关键挑战,使其成为功率和射频应用中下一代器件的理想平台。

GaN-on-SOI是一种新兴技术,它结合了氮化镓的高性能特性和SOI的电气隔离和机械优势,可显著提高器件效率和整体性能。

SOI上氮化镓(GaN-on-SOI)的关键优势在于其能够实现单片集成,通过将多种功能集成在单个衬底上,简化了器件架构。这种集成增强了可靠性,并支持更紧凑的设计。随着先进电子系统对更高效率和小型化的需求日益增长,SOI上氮化镓有望推动下一代半导体创新。键合SOI中的埋氧层(BOX)显著降低了寄生电容、漏电和串扰,从而实现更快的开关速度、更低的传导损耗和卓越的隔离度,这些对于高压功率转换至关重要。

Okmetic的(键合)氮化镓SOI衬底硅片专为优化氮化镓性能而设计,为开发功率和射频应用中的先进氮化镓器件提供了理想的平台。我们的衬底专为满足这些应用的要求而设计,同时提供卓越的电气隔离、低缺陷率、强大的热性能和机械强度。与我们的氮化镓硅衬底一样,我们的氮化镓SOI衬底硅片的所有参数均可定制,以满足客户应用的特定要求。可定制参数包括:

- 器件厚度、晶向、电阻率、Oi水平等

- 埋氧层(BOX)厚度

- 底层硅片厚度、晶向、电阻率、Oi水平等

无论是高压电源转换还是下一代射频系统,我们的硅片产品均可根据您的特定需求进行定制,以提供最佳性能。

GaN-on-SOI实现单片集成

将氮化镓器件单片集成在键合SOI硅片等先进衬底上,可以简化系统设计、提高性能并减少寄生损耗,为功率、射频和LED应用带来显著优势。

将氮化镓器件单片集成在键合SOI硅片等先进衬底上,可以简化系统设计、提高性能并减少寄生损耗,为功率、射频和LED应用带来显著优势。

目前大多数的氮化镓电源系统由多个分立芯片组成。譬如氮化镓HEMT之类的器件通常单独制造,然后组装到印刷电路板上。虽然这种模块化的方法很常见,但它会增加复杂性、增加成本,并可能限制整体系统的效率。

一种更有效的替代方案是单片集成,即将多个氮化镓功率器件集成在一个芯片上。半桥变换器就是一种受益于此法的拓扑结构,它包含一个低压侧开关和一个高压侧开关。这些开关在不同电压下工作,需要有效的电气隔离。单片集成可以通过先进的衬底和隔离策略(包括键合SOI晶圆中的埋氧层)来解决这个问题。这不仅简化了封装、降低了寄生损耗,还提升了紧凑型电源系统的性能。

Okmetic的键合SOI功率氮化镓衬底

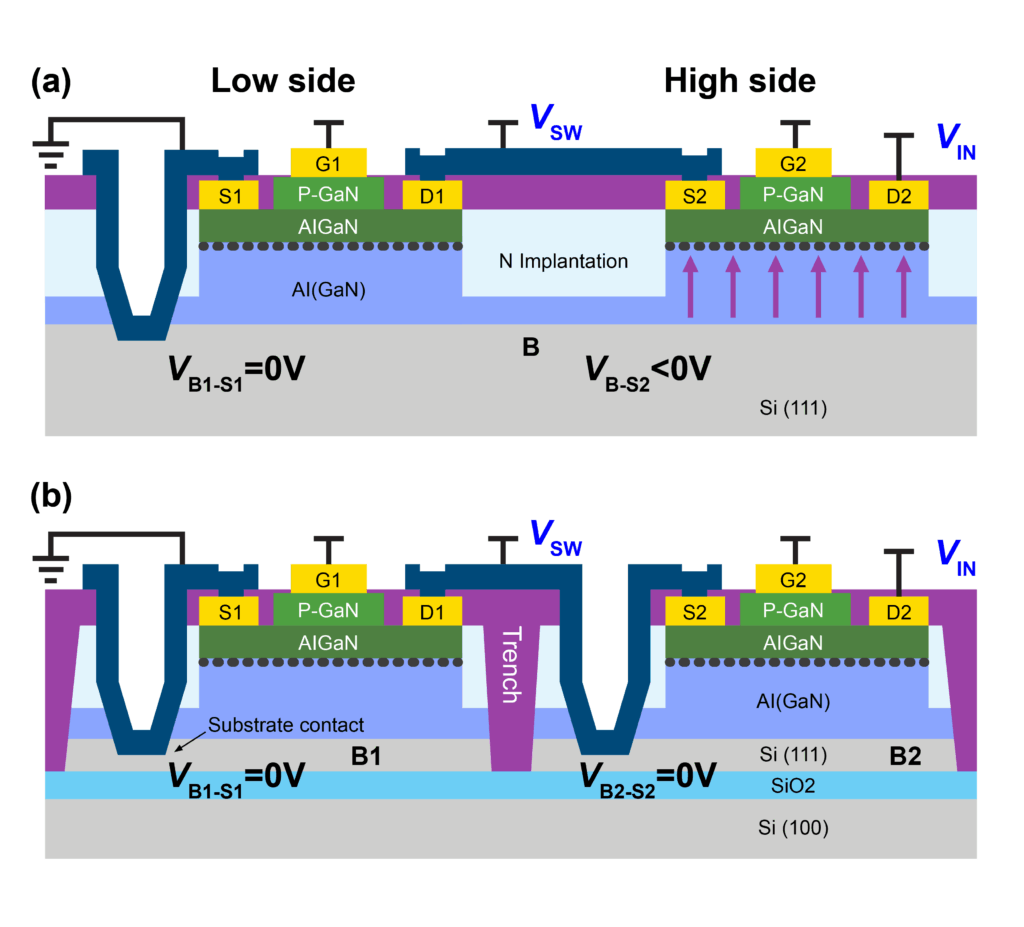

Okmetic的键合SOI功率氮化镓衬底硅片为全氮化镓集成电路提供了卓越的平台,它们最大限度地减少了串扰和背栅效应 [Li],从而提供了很好的电气隔离并增强了器件的性能。这一性能是通过使用SOI衬底进行氮化镓外延生长并结合沟槽隔离方法(图7)实现的,该方法完全隔离了高电子迁移率晶体管(HEMT)及其各自的硅器件层。通过将源极端子连接到各自的硅<111>器件层,可以完全消除背栅效应。

图7:在200mm(a)GaN-on-Si 和(b)GaN-on-SOI(带沟槽隔离)上构造带有增强模式低边和高边器件的单片集成半桥的横截面示意图。摘自 [Li]。

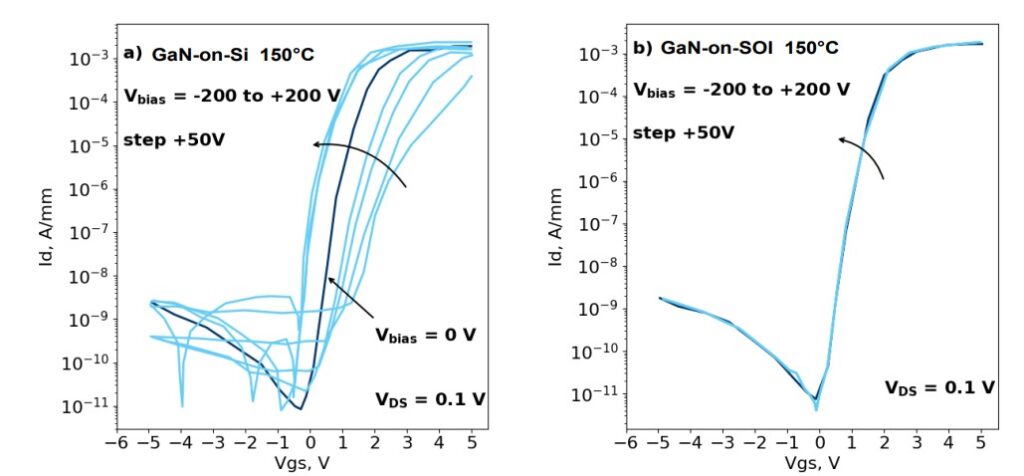

如图8所示,当相邻器件的SOI衬底偏置电压在-200V和200V之间时,传输特性几乎不会发生变化。相比之下,当硅衬底发生这种情况时,传输特性会发生辩护啊,导致器件性能下降。这种集成方法可以降低寄生电感、减小芯片尺寸、消除背栅效应,并最终提高电子效率。

图8:150°C下HEMT的传输特性,(a)采用常见的偏置电压为-200V至200V(硅上氮化镓)的硅衬底;(b)同时对相邻的硅<111>HEMT层施加不同电压(SOI上氮化镓),结果显示其影响极小。来源:[Li]。

Okmetic-IMEC的GaN-on-SOI功率器件合作

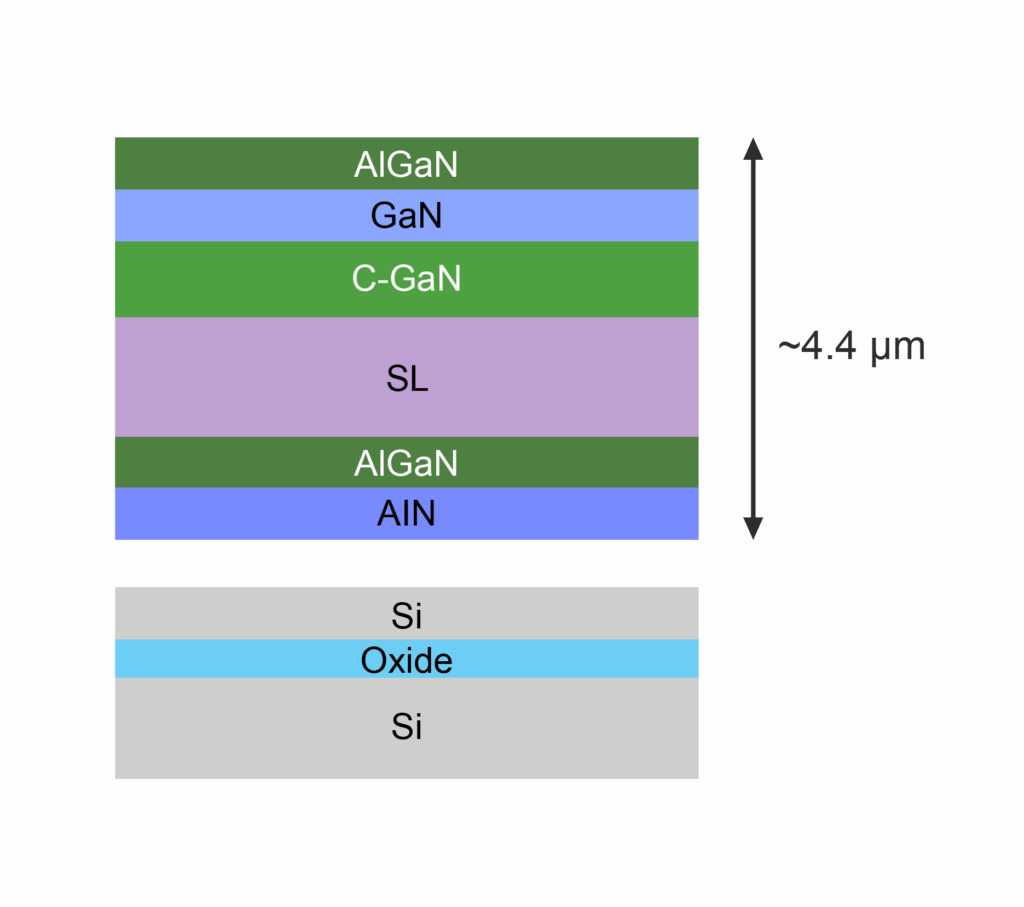

校际微电子中心(IMEC)近期开展的一项研究(2024)检验了Okmetic的氮化镓优化和未优化的SOI硅片,比较了它们的氮化镓生长、晶圆弯曲和稳定性的影响。IMEC成功在Okmetic的键合SOI硅片上生长了4.4 µm的氮化镓外延堆叠(图9)。研究结果强调了衬底诱导的机械稳定性在热应力和机械应力条件下实现高质量氮化镓外延的关键作用。

图9:IMEC在Okmetic的氮化镓SOI衬底上生长的合格外延堆叠。

氮化镓优化和未优化的SOI硅片在器件、埋氧层以及底层硅片厚度方面均具有相同的规格。两种晶圆均采用了<111>晶向,该晶向以提高硅片的耐用性而闻名。两种晶圆的主要区别在于氮化镓优化的SOI硅片,其底层硅片中的掺杂和氧间隙浓度更高。这种优化显著提高了晶圆在高温氮化镓生长过程中的坚固性和稳定性,为氮化镓外延提供了理想的平台,同时又不损害其结构的完整性。

氮化镓优化的SOI硅片在高温氮化镓生长过程中的稳健性和稳定性为氮化镓外延提供了理想的平台,同时又不影响其结构的完整性。

Okmetic-IMEC的GaN-on-SOI电气测试

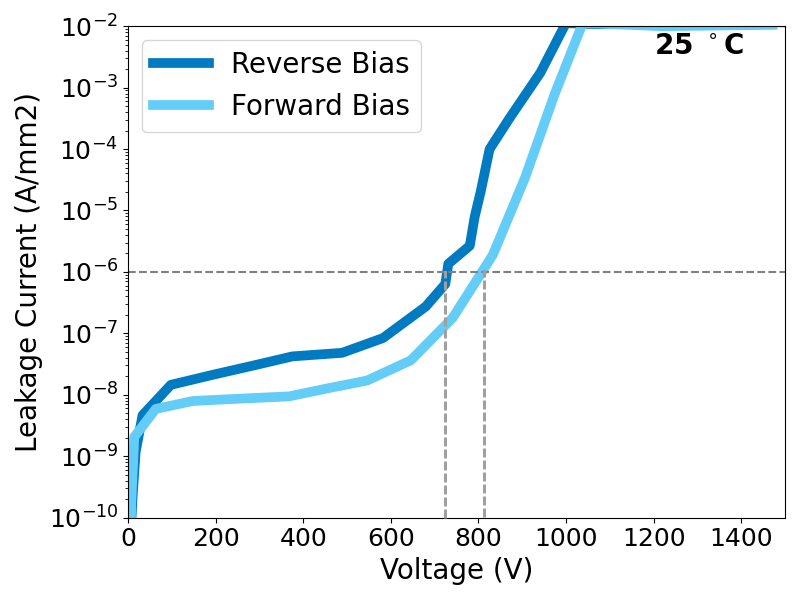

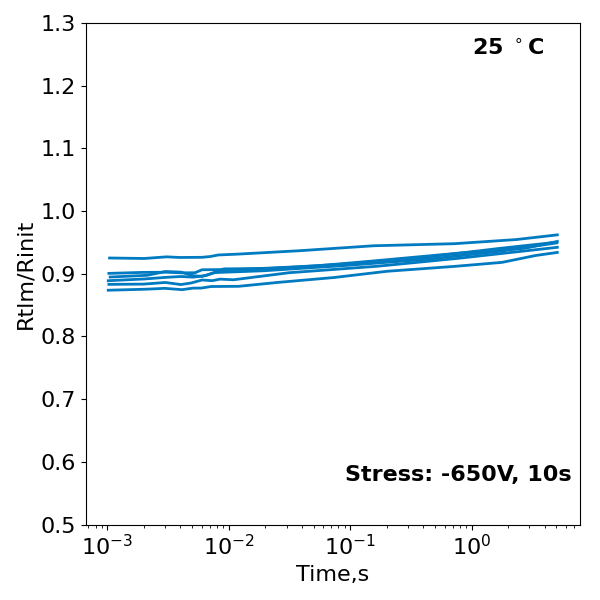

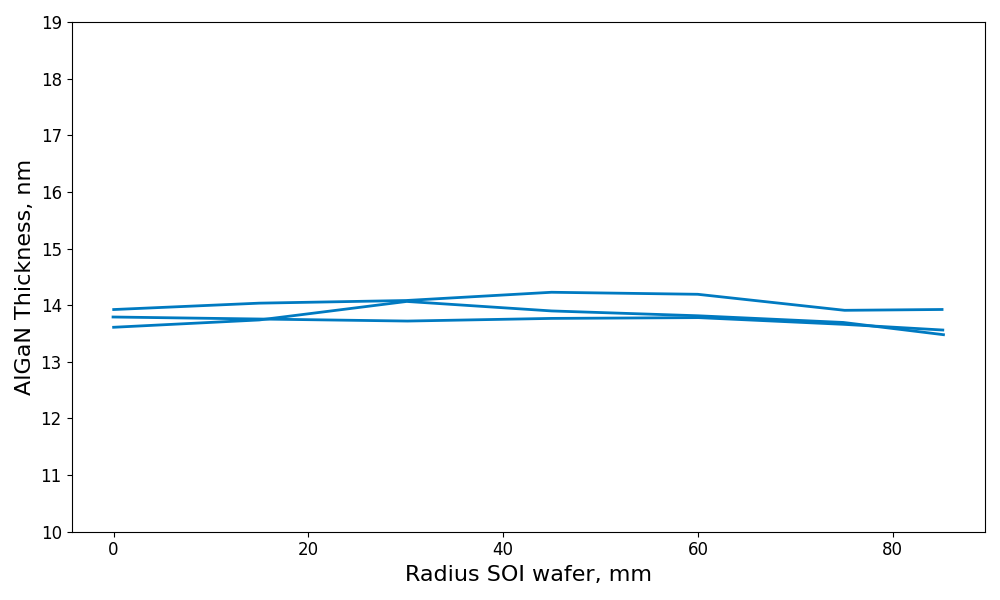

电气测试证实了该晶圆适用于高性能氮化镓器件,其漏电流低、缓冲击穿电压高(反向750V、正向850V),且捕获电荷效应极小,色散测量结果证实了这一点(图10a和10b)。此外,厚度变化极小的均匀AlGaN覆盖层(图10c)确保了氮化镓HEMT器件具有稳定的二维电子气(2DEG)特性和可靠的阈值电压,从而支持先进功率应用中的长期可靠性和性能。

电气测试证实了晶圆适用于具有低漏电流、高缓冲击穿电压和最小捕获电荷效应的高性能氮化镓器件。

图10a:Okmetic的功率氮化镓SOI衬底硅片用作氮化镓外延平台,在IMEC对小面积样品(0.01 mm2)进行缓冲层击穿电压测量期间,在反向偏压(25°C)约750V和正向偏压850V时实现了10-6 A/mm2的极低漏电流。

图10b:IMEC对Okmetic功率氮化镓SOI衬底硅片(用作氮化镓外延平台)进行的缓冲色散测量表明,捕获电荷效应极小。观察到的最小曲线加宽凸显了器件的优异性能。

图10c:X射线反射法测量AlGaN覆盖层随晶圆半径的厚度变化。AlGaN覆盖层对于器件性能很关键,因此1nm内的变化极其重要。

GaN-on-SOI对射频器件的适用性

Okmetic的键合SOI氮化镓衬底硅片为射频氮化镓器件的应用提供了显著优势,包括单片集成能力、低寄生电容、降低衬底损耗、高电气隔离度,以及关键的与标准CMOS集成工艺的兼容性,这些特性在高频射频系统中非常有价值。研究 [Tham]、[Jiang] 表明,SOI衬底可以减少垂直泄露并提高氮化镓器件的外延层质量。可以通过调整埋氧层厚度和选择器件和处理晶圆参数来定制衬底架构,以满足射频元件的严苛性能标准。这些因素使单片集成成为可能。当使用Okmetic的键合SOI射频氮化镓衬底硅片时,它可以支持进一步改进电路的紧凑性并改善整体射频系统的性能。

Okmetic的键合SOI氮化镓衬底硅片可实现单片集成,具有低寄生电容和高电气隔离度,为高频射频氮化镓器件提供更好的性能并提升其紧凑性。

结论

在对更高效率、更好热管理和经济高效的微缩需求推动下,硅基氮化镓(GaN-on-Si)技术在射频和功率应用中变得越来越重要。在2020年至2024年间,Okmetic已成功交付约50万片衬底产品,展现出其解决方案的强大市场接受度和可靠性。

硅衬底为氮化镓器件提供稳定的性能,以及无与伦比的成本效益、可扩展性和环境效益,而键合SOI衬底则为集成和增强器件性能开辟了新的可能性。要实现高质量、可靠的硅基氮化镓(GaN-on-Si)和SOI基氮化镓(GaN-on-SOI)器件,需要全面性地解决多个关键晶圆地特性。优化硅晶向、晶圆厚度、间隙氧浓度、边缘和电阻率对于控制机械应变、最大限度地减少晶圆翘曲和滑移,以及提高器件性能非常重要。每个参数都发挥着独特的作用。因此,全面优化晶圆特性是实现稳定、高产的氮化镓生长工艺的关键,以满足射频和功率电子应用的特定需求。

Okmetic持续开发针对氮化镓优化的硅和SOI衬底,并通过近期IMEC研究等合作项目验证,彰显出公司致力于推动下一代氮化镓技术发展的决心。Okmetic衬底可根据特定期间需求定制晶圆参数,为推进功率转换和射频通信提供稳健可靠的平台。

本白皮书中使用的参考文献列表可参见供下载的PDF版本。