图案化硅片:DRIE和光刻技术

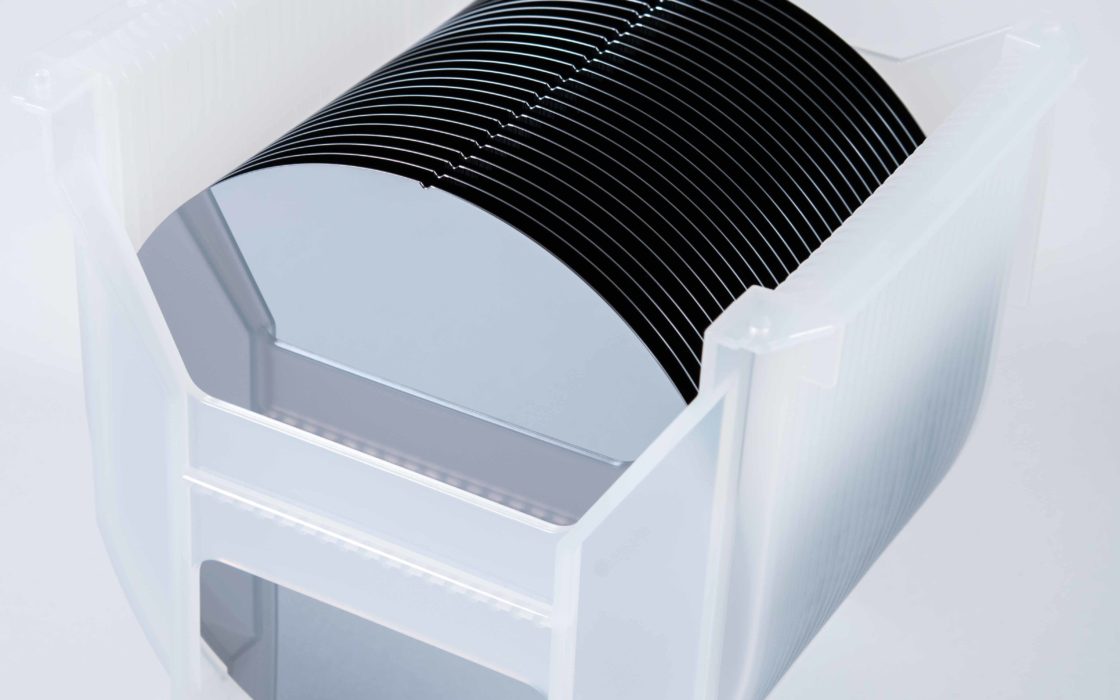

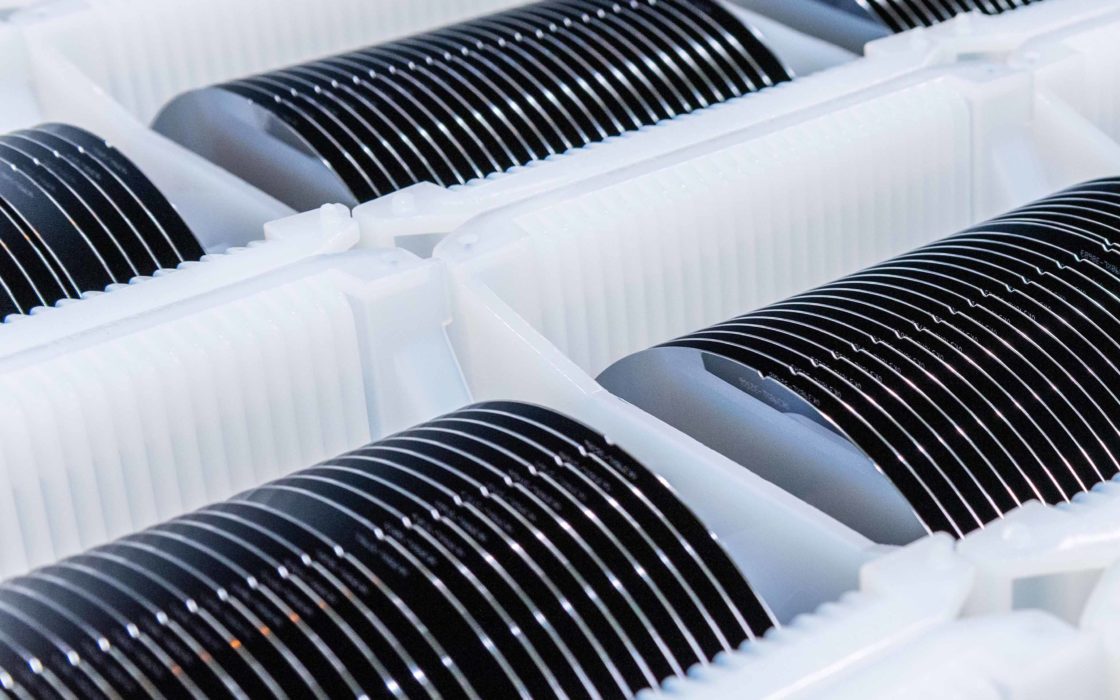

具有内置图案和埋腔(C-SOI®)的Okmetic单抛片(SSP)、双抛片(DSP)和SOI硅片可以优化MEMS和射频滤波器的制造。Okmetic全自主制造的工艺涵盖了晶体生长、切片、光刻、DRIE和熔焊键合SOI硅片,确保了硅片产品的最高品质和更短的出货时间。

观看视频了解图案化硅片和C-SOI®硅片的生产

MEMS和射频滤波器设备市场对交钥匙定制硅片和定制硅片结构的需求不断增加。Okmetic的单抛片(SSP)、双抛片(DSP)和SOI硅片具有内置图案和腔体(C-SOI®),经过定制能够无缝满足客户设备的设计和工艺,所有的硅片产品都是Okmetic自主制造的。这种生产模式不仅能够实现更复杂的设备设计和更短的出货时间,还能够显著提高硅片产品的质量和可靠性。图案化硅片的品质和洁净度标准与体硅晶圆相同。

经过定制的硅片能够无缝匹配客户的设备设计和工艺,图案化硅片能够优化MEMS和射频滤波器的制造。

这种现成的硅基衬底消除了MEMS和射频滤波器制备工艺的复杂性,为设备制造商创造了真正的价值,让制造商能够节约自身产能并专注于其他更关键的工艺步骤。

图案化是一个额外的工艺步骤,它可以更加简化多种设备器件的制造,诸如压力传感器、硅麦克风、喷墨头等微流体设备、惯性传感器、IC和 MEMS工艺集成、PMUT和CMUT等超声波换能器、微镜等光学设备、计时设备、其他谐振器和封帽硅片。

硅片加工的所有步骤都全面考虑到器件设计的需求

为了拥有性能更好的设备和更优化的工艺,我们必须根据设备和工艺的需求定制硅片及其参数。此外,对于单抛片(SSP)、双抛片(DSP)和带有内置图案和埋腔的SOI硅片,客户的设备设计及其工艺为Okmetic的硅片设计和定制加工奠定了基础。硅片加工的每一步都需要切实考虑到客户的设备设计和工艺需求,从晶体生长、切片、SOI加工到光刻图案化及深反应离子刻蚀(DRIE)。

我们的产品质量优于参考工艺

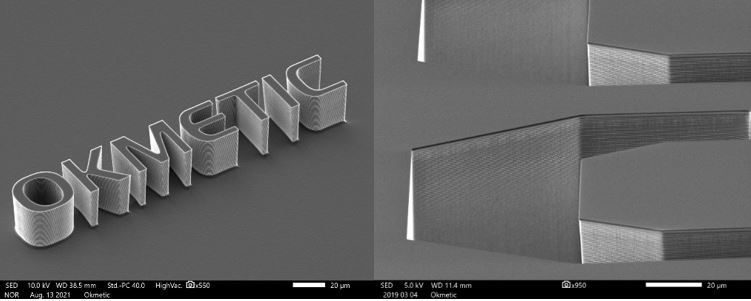

生产高性能硅片的关键是最先进的制造工艺和大量的专业知识。Okmetic几年前开始的图案化生产线正是因此而成立的,从出色的硅片质量和可靠性也能看出我们的专业。就裸片良率而言,Okmetic的图案化工艺在AVI缺陷率方面明显优于参考工艺。此外,在刻蚀深/浅腔或复杂结构时,DRIE工艺实现了极高的均匀性,这可以从客户设备表现出的更高性能和精度中看出。

在刻蚀深/浅腔或复杂结构时,实现了极高的均匀性。

图案化生产线的工具和工艺专为无缺陷的腔体和表面而设计:

- 自动化处理硅片和真空背面

- 通过硅片的红外对准功能使背面对准标记变得多余

- 使用集成镭射代码阅读器,实施硅片级可追溯性管理

- 在刻蚀步骤之间最大限度地减少硅片暴露于外部环境的可能性

- 改进 AVI 和键合缺陷检测

优异的刻蚀精度

- 垂直侧壁的选项

- 高刻蚀速率及有效的刻蚀停止

- 刻蚀中的整体行为是可预测且一致的

- 刻蚀结构出色的精度和均匀性

如何制造内置图案的硅片

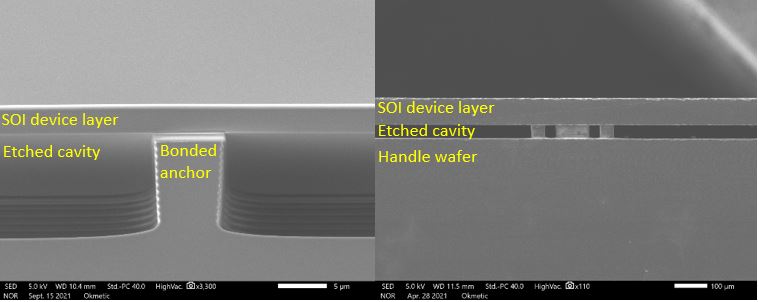

制造具有内置图案和空腔的硅片的时候,须要在图案化步骤中生长掩膜氧化物以保护硅片表面,然后在硅片表面涂上光敏材料。抗蚀剂所需的区域用紫外线曝光,接着进行显影和蚀刻。接着,使用自动检测工具查验空腔和器件薄膜等图案化特征是否存在缺陷。将封帽硅片键合在具有内置图案的硅片顶部,再减薄至C-SOI®硅片所需的厚度。超声波可以检验硅片粘合的界面是否存在缺陷。C-SOI®硅片的图案化实现穿过顶层硅片的电流馈通。

全新的图案化生产线自2019年开始启用

在2017和2018年期间,Okmetic数十年深耕晶体生长、切片和SOI技术等方面,其专业度和光刻图案化以及深反应离子蚀刻(DRIE)的能力相得益彰。与此同时,万塔工厂扩建了1000多平方米的洁净室和一条专门用于单抛片(SSP)、双抛片(DSP)和SOI硅片图案化的新生产线。全新图案化生产线的第一批订单于2019年2月交付。在此之前,图案化工艺于2005年至2018年外包。

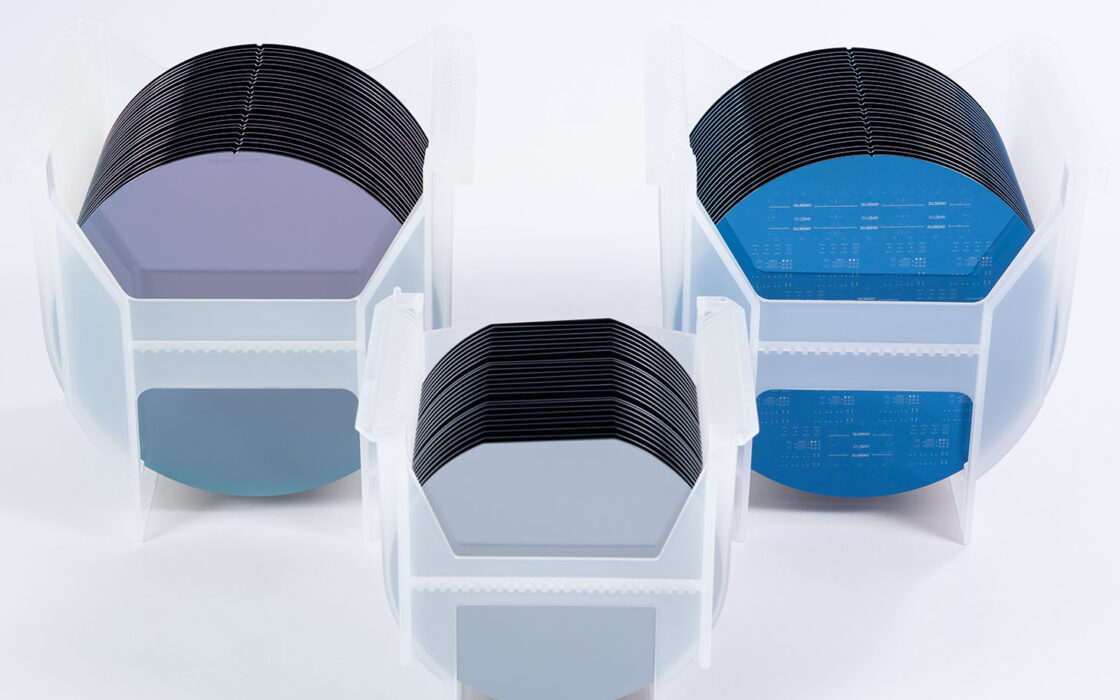

C-SOI®硅片规格

下表列出了Okmetic的常规C-SOI®硅片的规格。我们的C-SOI®硅片通常都是为客户量身定制的,欢迎联系我们的销售和技术支持以获取更多详细资讯。

| C-SOI®硅片直径 | 150 mm, 200 mm |

器件层规格

| 晶体生长方式 | Cz, MCz, A-MCz® |

| 晶向 | <100>, <110>, <111> |

| N 型掺杂剂 | 锑、磷 |

| P 型掺杂剂 | 硼 |

| 电阻率 | 从<0.001到>7000 欧姆-厘米* *电阻率范围因掺杂剂和晶向而异 |

| 器件层 / 薄膜厚度 | 2微米到>200微米 |

| 器件层 / 薄膜厚度公差 | 通常±0.5微米,EC-SOI硅片中低至±0.2微米 |

埋氧层 (BOX) 规格

| 类型 | 热氧化物生长于底层硅片或器件层或同时 |

| 厚度 | 0.3微米到5微米,通常在0.5微米到2微米之间 |

衬底层规格

| 晶体生长方式 | Cz, MCz, A-MCz® |

| 晶向 | <100>, <110>, <111> |

| N 型掺杂剂 | 锑、磷 |

| P 型掺杂剂 | 硼 |

| 电阻率 | 从<0.001到>7000 欧姆-厘米* *电阻率范围因掺杂剂和晶向而异 |

| 底层硅片厚度 | 200 mm:380–675微米 150 mm:380–725微米 |

| 底层硅片厚度公差 | ±5微米 |

| 背面 | 抛光或氧化物刻蚀 |

腔体规格

| 空腔位置 | 底层硅片或器件层,或埋氧层 |

| 腔体深度(硅体中) | 2–500微米 |

| 最小CD | 2微米 |

| 最大腔体跨度长度和薄膜厚度 | 采用标准C-SOI®工艺,<40:1微米 |

上表面对齐标记

| 对准精度,埋腔到上表面对准标记 | ±1微米 |

| 标记设计 | 根据客户需求 |