E-SOI® wafers – Enhanced SOI

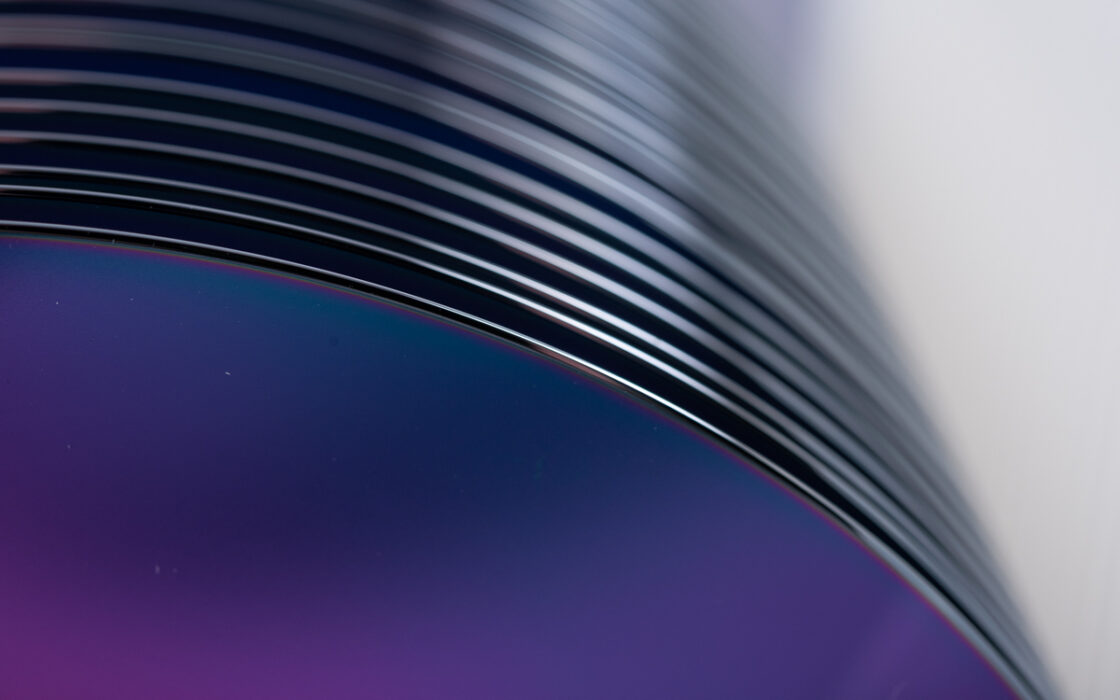

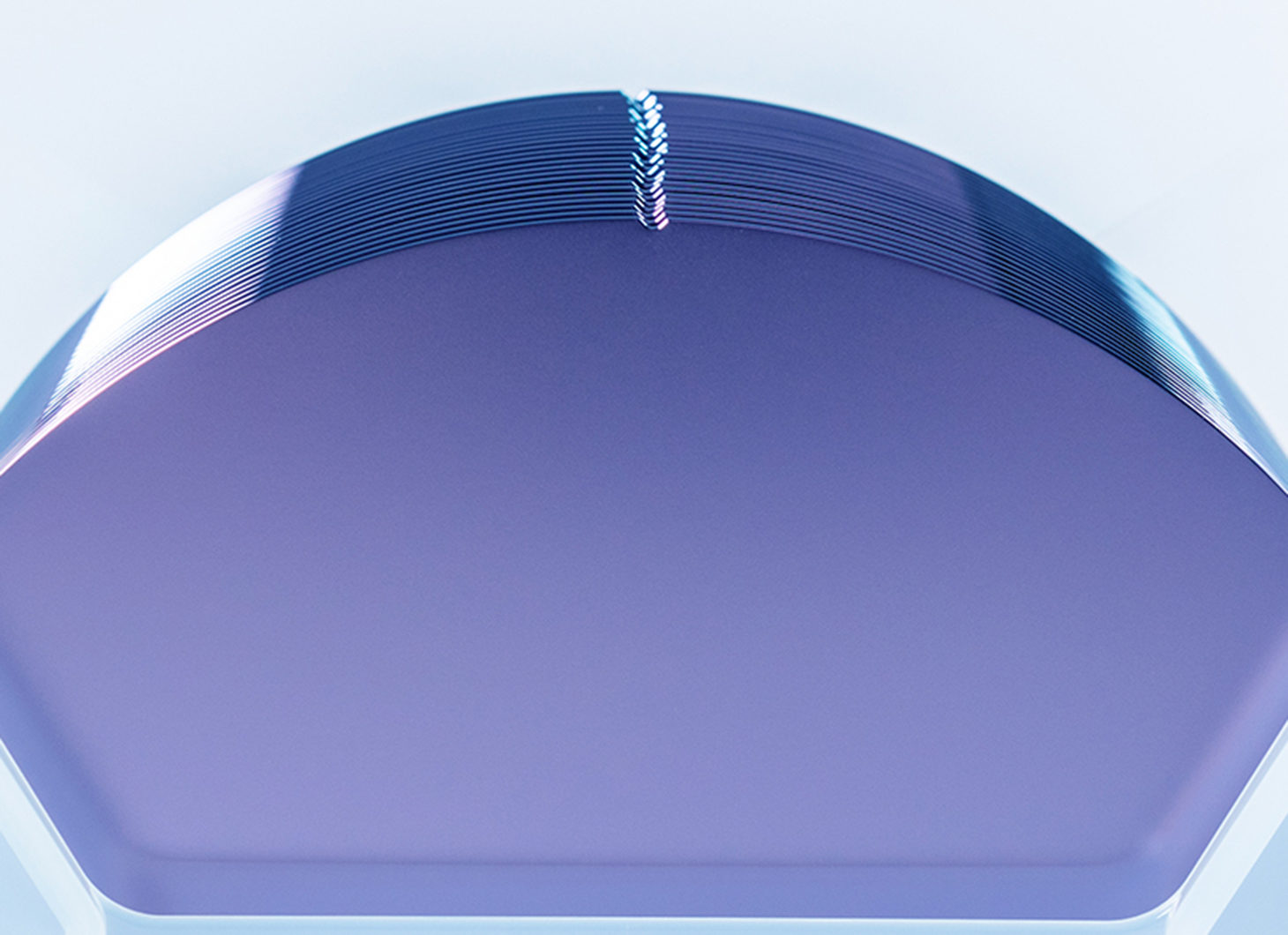

Okmetic E-SOI® is an enhanced, highly uniform Silicon On Insulator wafer with tight ±0.1 µm thickness tolerance. The combination of thicker device layer and significantly lower device layer thickness variation makes E-SOI® an ideal platform for demanding MEMS and sensor devices as it enables device designs out of reach with traditional techniques in addition to improved device performance and precision.

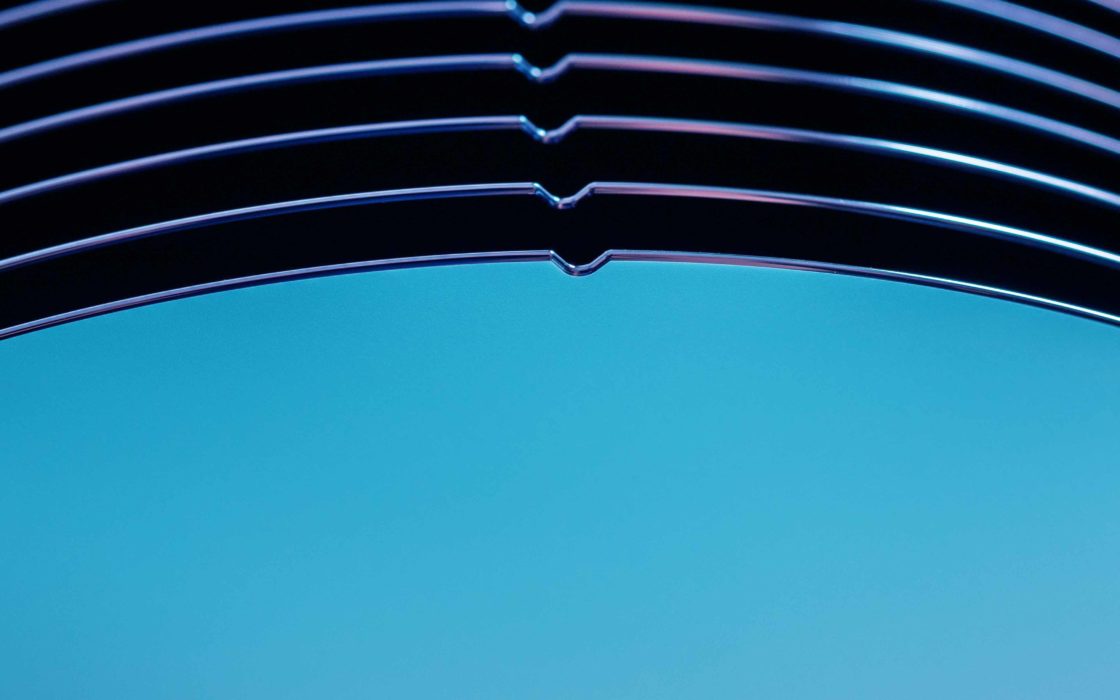

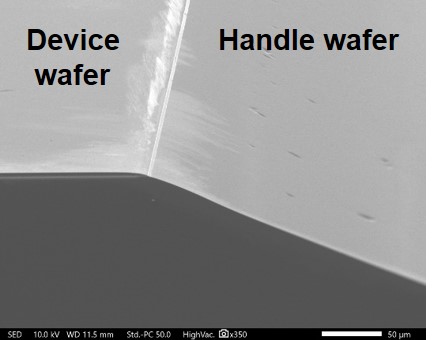

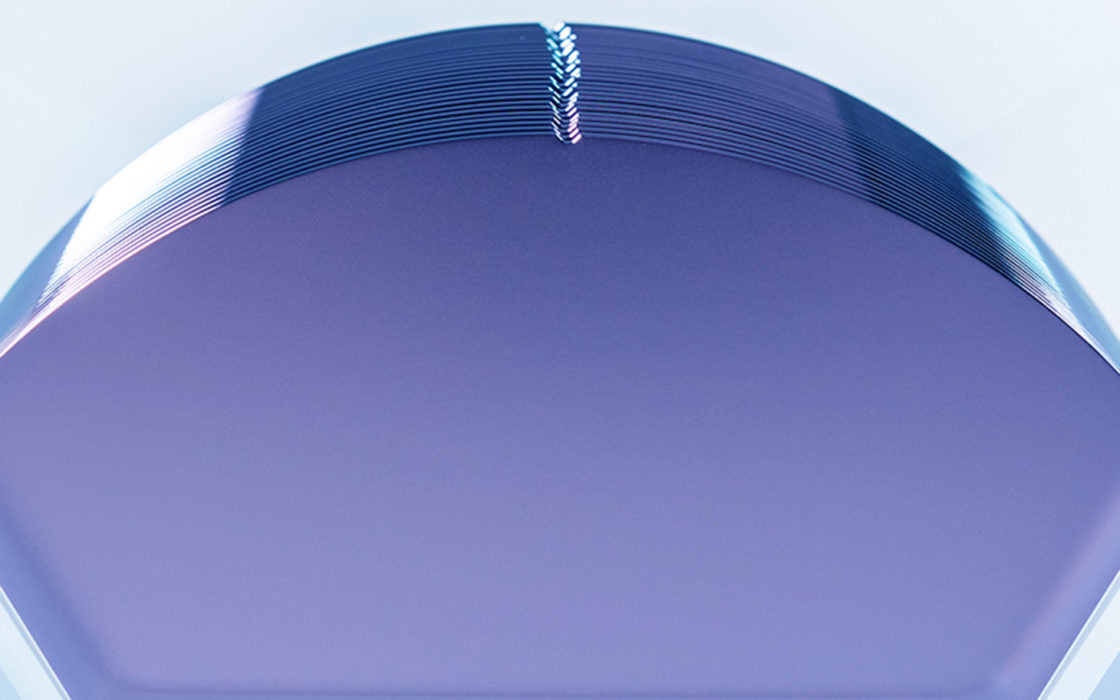

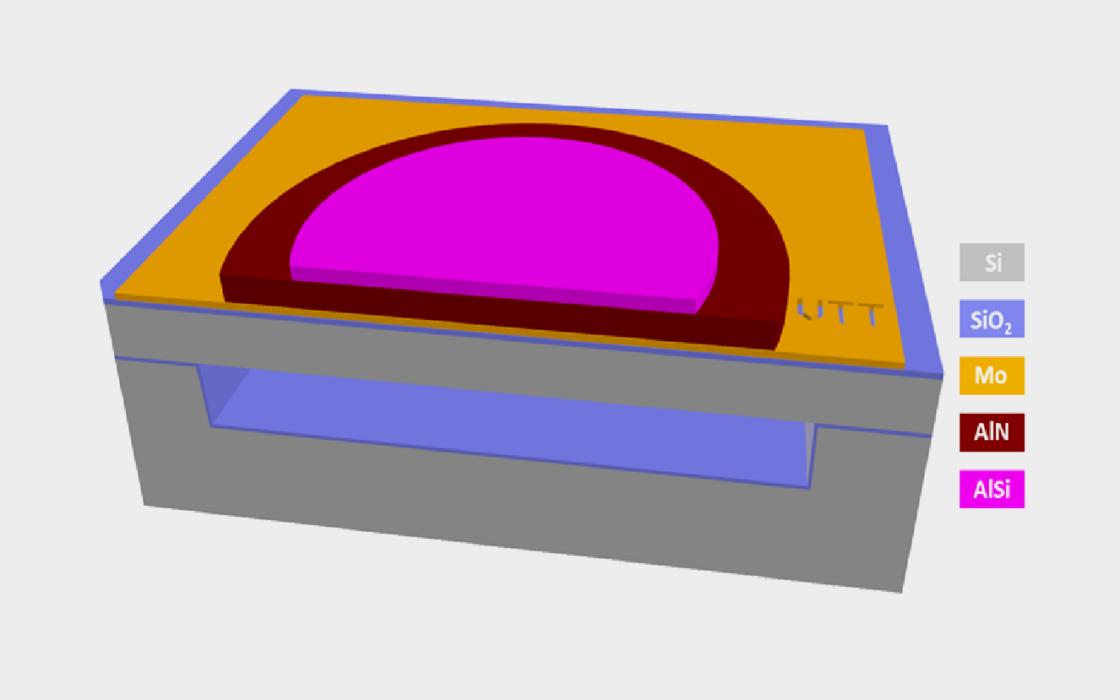

Okmetic E-SOI® is an enhanced bonded Silicon On Insulator wafer, which has buried oxide (BOX) layer between a bottom handle wafer and a top silicon wafer that is thinned with extreme precision to achieve best-in-class device layer thickness uniformity. Enhanced SOI (E-SOI®) wafer’s device layer can be made thicker and more uniform than with competing SOI technologies.

E-SOI® wafer’s best-in-class device layer thickness uniformity enables the most demanding device designs

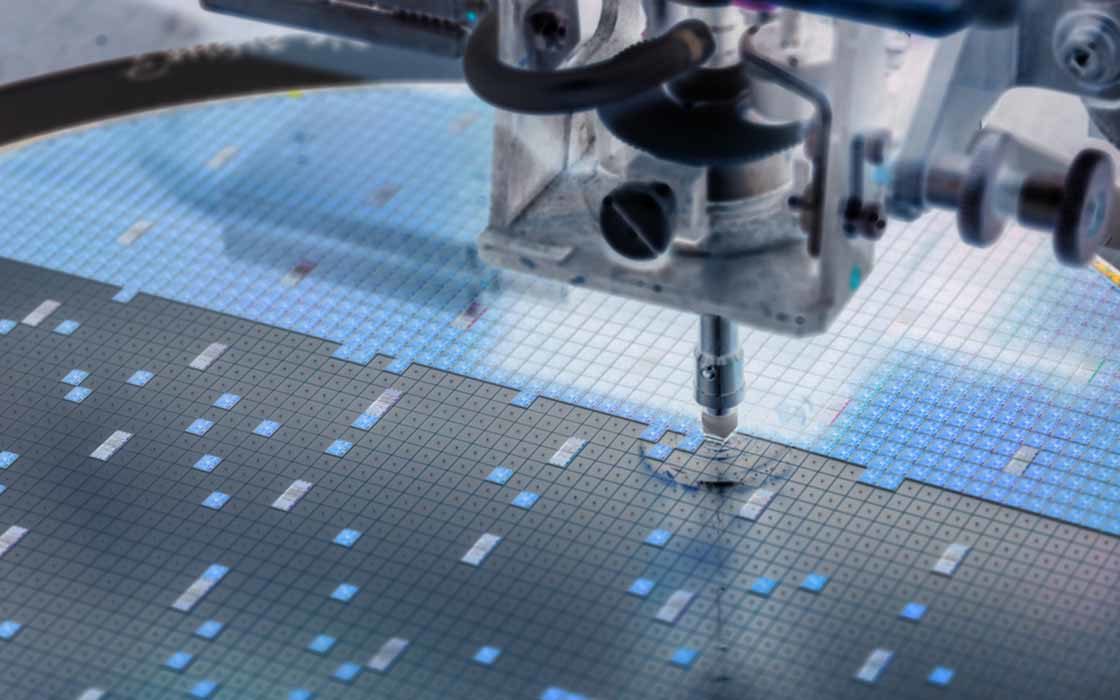

Typically MEMS sensors are built on the device layer whilst the buried oxide (BOX) is an excellent electric insulating layer and an effective etch stop. The BOX layer can also act as a sacrificial layer for complex components and released structures. The handle wafer supports the structure, but can also be utilized in sealing the structure or as part of the sensing element.

Enhanced SOI wafer for demanding device needs

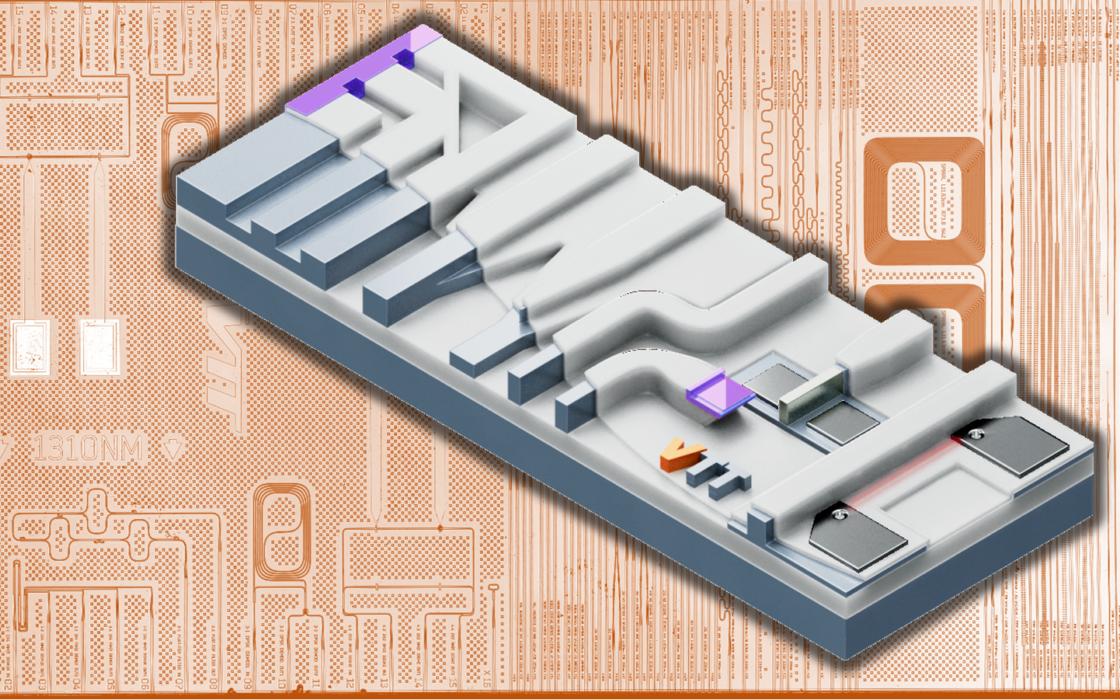

Due to its thicker and highly uniform device layer, Okmetic E-SOI® wafer is an ideal platform for demanding applications such as silicon photonics, silicon timing devices, and high-precision silicon-based MEMS and sensors and more. E-SOI® wafers are used especially in silicon photonics, which is a rapidly growing field of technology including devices such as optical transceivers, optical sensors and LiDAR system devices. E-SOI® wafers have found to provide excellent waveguide for silicon photonics. Okmetic also suppliers Power Management SOI wafers that combines E-SOI® benefits to other power management optimized wafer characteristics.

Okmetic E-SOI® has unprecedented properties. The device layer thickness of Enhanced SOI is freely adjustable between 1.0 µm and >100 µm and the thickness tolerance is as low as ±0.1 µm (200 mm wafer) or ±0.2 µm (150 mm wafer). Also the buried oxide layer thickness is freely adjustable between 0.5 µm and >5 µm.

E-SOI® wafer is an ideal platform e.g. for silicon photonics and timing devices, and high-precision MEMS sensors

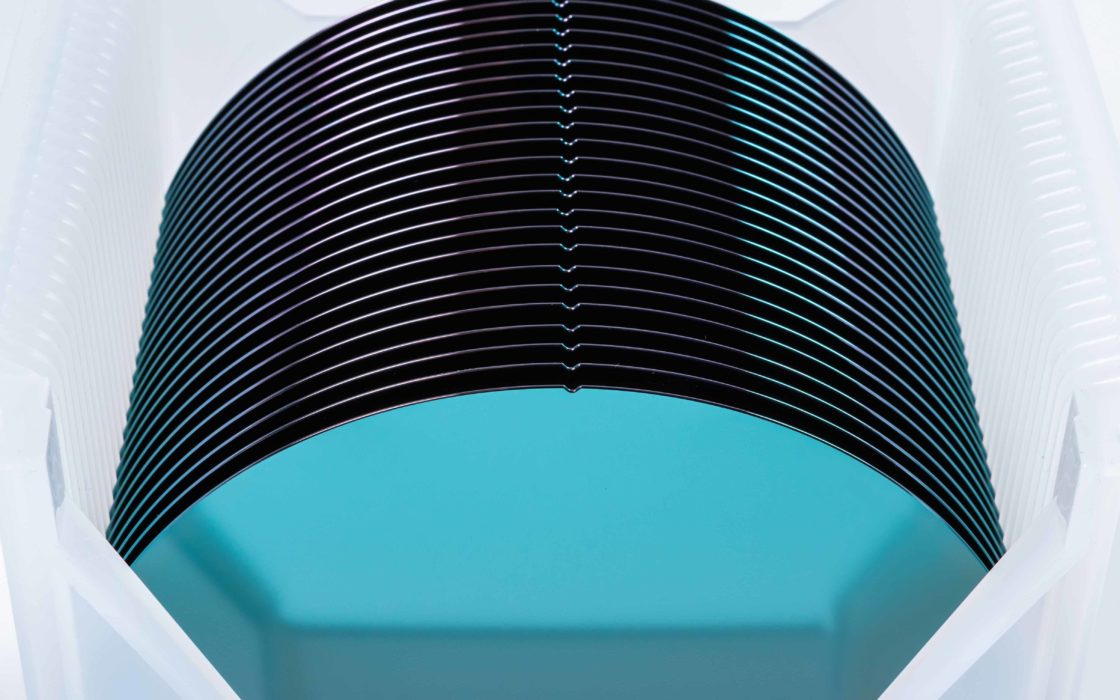

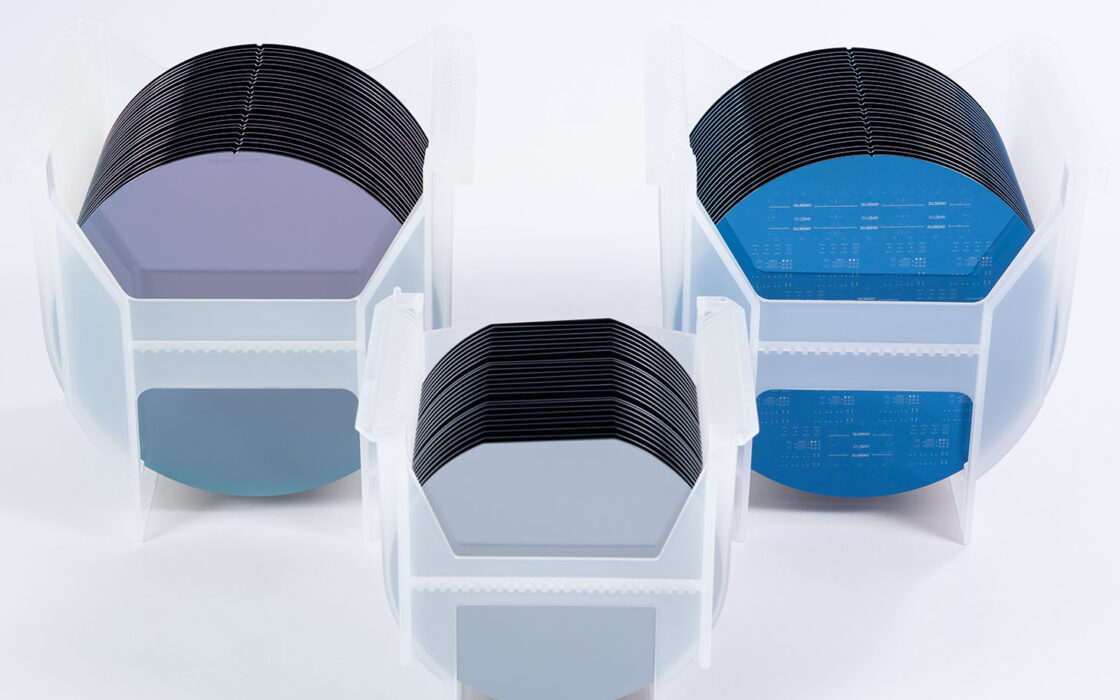

As with other Okmetic Silicon On Insulator wafers, the E-SOI® wafer can be customized to match your exact device and process needs. Okmetic has the widest selection of silicon wafers in the market, and our sales and technical support are happy to help in customization and selection of wafer parameters to find an optimal solution for your needs. E-SOI® wafers are also available as Terrace Free SOI wafers.

Typical SOI specifications

| Growth method | Cz, MCz, A-MCz® |

| Diameter | 200 mm, 150 mm |

| Crystal orientation | <100>, <110>,<111> |

| N type dopants | Antimony, Phosphorus |

| P type dopants | Boron |

| Resistivity1 | From <0.001 to >7,000 Ohm-cm |

| Device layer thickness2* | From 1 μm to >200 μm Tolerance ±0.5 μm (standard BSOI), ±0.3 μm (0.3 SOI), ±0.1 μm (E-SOI®, Power Management SOI), ±0.5 μm or lower (C-SOI®) |

| Buried oxide layer thickness3 | From 0.3 μm to >5 μm |

| Handle wafer thickness4 | 200 mm: 300 μm to 950 μm 150 mm: 300 μm to 950 μm |

| Back surface | Polished or etched |

| Terrace area | Standard or Terrace Free (Available for 200 mm BSOI, E-SOI® and Power Management SOI) |

2Other thicknesses possible with certain limitations. 150 mm E-SOI® tolerance ±0.2 µm

3Type: thermal oxide. Typically 0.5 μm to 2 μm. >5 μm BOX possible with certain limitations.

4200 mm: typically 500-725 μm, 150 mm: typically 380-675 μm. ±3 µm tolerance for demanding devices

*Possibility also for two device and buried oxide layers with different thicknesses.

Fully CMOS compatible wafer surface quality and cleanliness requirements

Significantly lower device layer thickness variation enabling true innovation

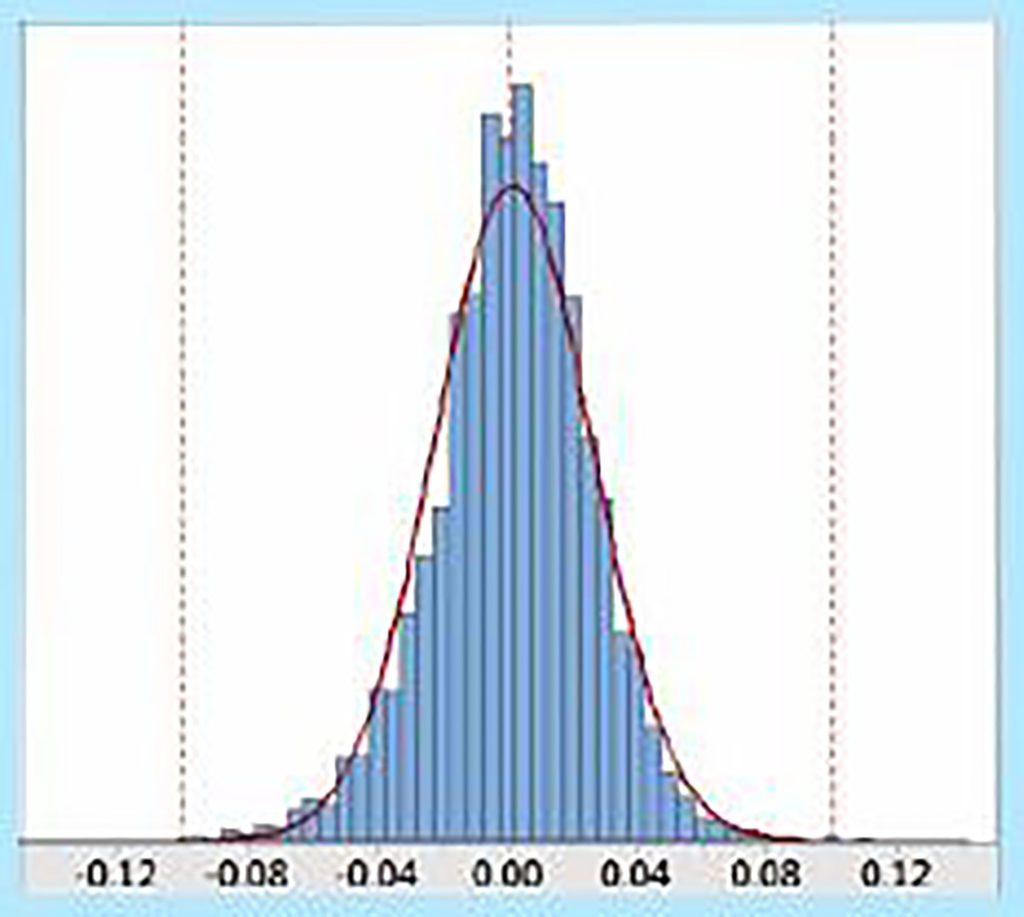

The core benefit of E-SOI® wafer compared to standard BSOI wafer is superior device layer thickness uniformity. E-SOI® thus enables more advanced device designs than can be achieved with traditional BSOI technologies let alone with bulk silicon micromachining.

Device layer thickness capability of E-SOI® wafers

Deviation from target thickness (µm)

E-SOI® wafer is an advanced solution with multiple benefits:

- More freedom to device design than with competing technologies

- Improved device performance and precision

- Reduced device size and cost

- Improved device yield